# SERVICE MANUAL AT&T SYSTEM 75 MAINTENANCE SUPPORT

555-200-108IS Issue 1, August 1984

Copyright \* 1984 AT&T Technologies All Rights Reserved

Printed in U.S.A.

To order copies of this manual,

AT&T Information Systems 800-526-0735 Call:

Order: Document No. 555-200-108IS

To comment on this manual,

AT&T Technologies, Inc.

800-334-0404

8AM-4PM Eastern Time Monday through Friday

In North Carolina, call 919-727-3167

# CONTENTS

|                                             |         |      | Page     |

|---------------------------------------------|---------|------|----------|

| INTRODUCTION                                |         | <br> | <br>. 1  |

| SWITCH HARDWARE                             |         | <br> | <br>. 2  |

| SWITCHING NETWORK                           |         | <br> | <br>. 3  |

| TDM Bus                                     |         | <br> | <br>. 3  |

| Functional Description                      |         | <br> | <br>. 3  |

| Physical Characteristics                    |         | <br> | <br>. 4  |

| Electrical Characteristics                  |         | <br> | <br>. 4  |

| Intelligent Ports                           |         | <br> | <br>. 7  |

| Common Circuitry                            |         | <br> | <br>. 7  |

| Line Ports                                  |         | <br> | <br>. 9  |

| Trunk Ports                                 |         | <br> | <br>. 16 |

| Service Circuits                            |         | <br> | <br>. 24 |

| SWITCH PROCESSING ELEMENT                   |         | <br> | <br>. 31 |

| 8-Bit On-Board Microprocessor A With Extern | nal RAM | <br> | <br>. 33 |

| 8-Bit On-Board Microprocessor B With Extern | al RAM  | <br> | <br>. 33 |

| Scanner Circuits                            |         | <br> | <br>. 34 |

| Clock Circuit                               |         | <br> | <br>. 34 |

| M Bus Interface Circuit                     |         | <br> | <br>. 34 |

| HIGH CAPACITY MINIRECORDER                  |         | <br> | <br>. 43 |

| General                                     |         | <br> | <br>. 43 |

| Tape Cartridge                              |         | <br> | <br>. 43 |

| High Capacity Minirecorder Circuit Packs .  |         | <br> | <br>. 43 |

| APPLICATIONS PROCESSOR INTERFACE            |         | <br> | <br>. 47 |

| MAINTENANCE CIRCUIT                         |         | <br> | <br>. 56 |

| General                                     |         | <br> | <br>. 56 |

| SPE Monitoring and GO-TO-SLEEP Control      |         | <br> | <br>. 56 |

| System Interactions                         |         | <br> | <br>. 57 |

| Maintenance Circuit Pack                    |         | <br> | <br>. 59 |

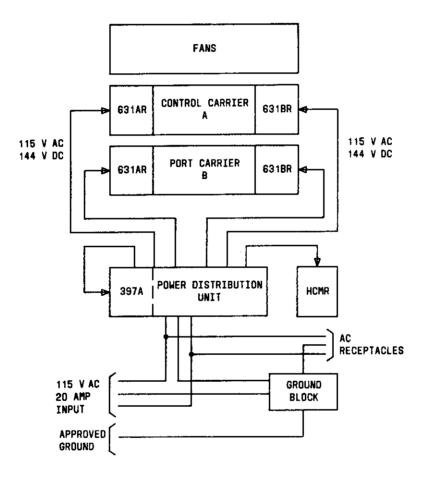

| POWER SYSTEMS                               |         | <br> | <br>. 63 |

| AC Power                                    |         | <br> | <br>. 64 |

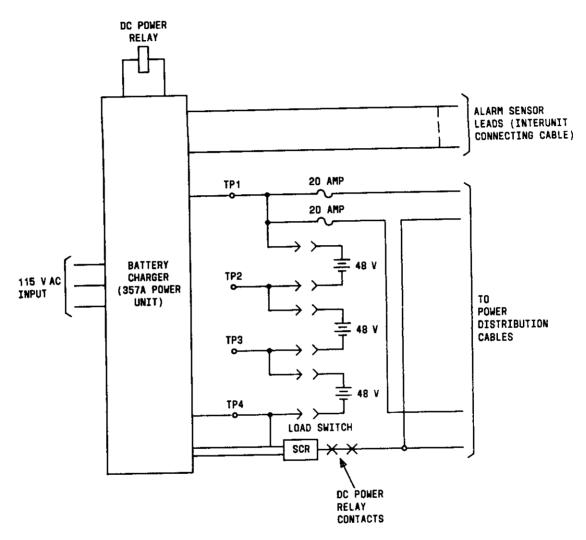

| Battery Backup                              |         | <br> | <br>. 65 |

| Power Units                        | p.  |

|------------------------------------|-----|

| SYSTEM SOFTWARE                    | 69  |

| SWITCHED SERVICES SOFTWARE         | 69  |

| Step-By-Step Call Description      | 69  |

| ADMINISTRATIVE SOFTWARE            | 7   |

| MAINTENANCE SOFTWARE               | 7   |

| High-Level Maintenance Software    | 7:  |

| System Initialization and Recovery | 72  |

| Software Maintenance               | 73  |

| Dynamic System Configuration       | 73  |

| Hardware Diagnostics and Tests     | 74  |

| Maintenance Load Regulation        | 7   |

| Low-Level Maintenance Software     | 7   |

| TROUBLE CLEARING AIDS              | 70  |

| GENERAL                            | 76  |

| ALARM LOG                          | 76  |

| ERROR LOG                          | 76  |

| Display Form                       | 77  |

| Display Output                     | 79  |

| Error Codes and Aux Data           | 81  |

| MAINTENANCE COMMANDS               | 102 |

| Test Commands                      | 102 |

| Reset Commands                     | 119 |

| Busyout Commands                   | 120 |

| Release Commands                   | 123 |

| Display Commands                   | 123 |

| List Configuration Commands        | 124 |

| Miscellaneous Commands             | 128 |

| Test Descriptions                  | 129 |

| Error Codes                        | 4(  |

| FACILITIES ACCESS TEST             | 153 |

| ABBREVIATIONS AND ACRONYMS         | 157 |

|                                    |     |

# LIST OF FIGURES

| Figure 1.  | Communications Switch                                                                  | 2  |

|------------|----------------------------------------------------------------------------------------|----|

| Figure 2.  | TDM Bus Time Slot Generation                                                           | 3  |

| Figure 3.  | TDM Bus Wiring Diagram—Fully Loaded (4-Port Carrier and Control Carrier) Configuration | e  |

| Figure 4.  | Port Circuit Pack Common Circuitry                                                     | 7  |

| Figure 5.  | Unique Analog Line Circuitry                                                           | 9  |

| Figure 6.  | Unique Digital Line Circuitry                                                          | 11 |

| Figure 7.  | Unique Hybrid Line Circuitry                                                           | 14 |

| Figure 8.  | Unique MET Line Circuitry                                                              | 15 |

| Figure 9.  | Unique CO Trunk Circuitry                                                              | 17 |

| Figure 10. | Unique DID Trunk Circuitry                                                             | 19 |

| Figure 11. | Unique Tie Trunk Circuitry                                                             | 21 |

| Figure 12. | Unique Auxiliary Trunk Circuitry                                                       | 23 |

| Figure 13. | Tone/Clock Circuit                                                                     | 25 |

| Figure 14. | Tone Detector Circuit                                                                  | 28 |

| Figure 15. | Pooled Modem Circuit                                                                   | 29 |

| Figure 16. | Network Control Circuit                                                                | 32 |

| Figure 17. | Processor Circuit                                                                      | 35 |

| Figure 18. | Memory Circuit                                                                         | 39 |

| Figure 19. | Tape Control Circuit                                                                   | 42 |

| Figure 20. | High Capacity Minirecorder Circuit                                                     | 44 |

| Figure 21. | Interface 1 Circuit                                                                    | 48 |

| Figure 22. | Interface 2 Circuit                                                                    | 51 |

| Figure 23. | Interface 3 Circuit                                                                    | 55 |

| Figure 24. | Maintenance Circuit                                                                    | 60 |

| Figure 25. | Power Distribution Scheme for 2-Carrier Cabinets                                       | 63 |

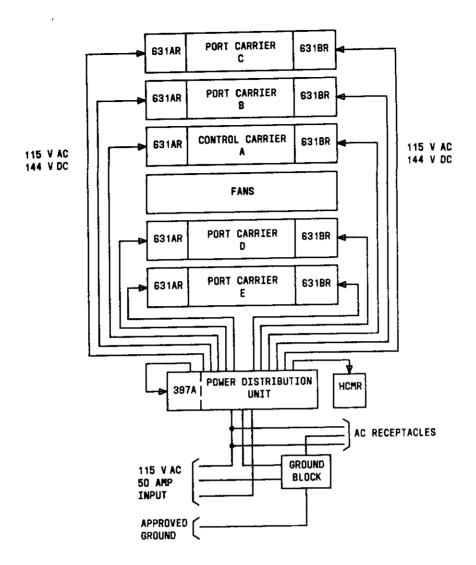

| Figure 26. | Power Distribution Scheme for 5-Carrier Cabinets                                       | 64 |

| Figure 27. | Battery Backup Circuit                                                                 | 65 |

| Figure 28. | Hardware Error Reports Form                                                            | 77 |

| Figure 29. | Typical Error Log Display Output                                                       | 80 |

| Figure 30. | Typical Demand Test Results                                                            | 03 |

| Figure 31. | Typical Busyout Command Results                                                        | 21 |

| Figure 32. | Set Time Form                                                                          | 24 |

| Figure 33. | Typical Initialization Causes Form                             | 124 |

|------------|----------------------------------------------------------------|-----|

| Figure 34. | Partial Example of Display Output for "List Configuration All" |     |

|            | Command                                                        | 126 |

| Figure 35. | Typical Software Configuration Report                          | 127 |

<del>-</del>

•

# LIST OF TABLES

| TABLE A. | Dedicated Time Slots For Tones |     | •   | • | •   | •  | • | • | • | • | • | • | ٠ |    | • | • | 5   |

|----------|--------------------------------|-----|-----|---|-----|----|---|---|---|---|---|---|---|----|---|---|-----|

| TABLE B. | Maintenance Circuit Pack Leds  |     |     | • | •   | ٠. |   |   |   |   |   |   |   | ٠. |   |   | 58  |

| TABLE C. | Hardware Category Entries .    |     |     |   |     | •  |   |   |   |   |   |   |   |    |   |   | 78  |

| TABLE D. | System Access Tones-Facilities | Acc | ess | т | est |    |   |   |   |   |   |   |   |    |   |   | 155 |

# INTRODUCTION

This manual is a backup document for the System Maintenance manual (555-200-105IS). It includes information necessary to understand the overall system operation and to develop more complex trouble locating procedures than those covered in Manual 555-200-105IS.

# **ORGANIZATION**

The information presented in this manual is divided into the following sections:

- SWITCH HARDWARE—Provides a functional description of the System 75 switch hardware. The switch hardware includes the switching network, switch processing element, high capacity minirecorder, applications processor interface, maintenance circuit pack, and power supply.

- SYSTEM SOFTWARE —Describes the system software resources including switched services software, administration software, and maintenance software.

- TROUBLE CLEARING AIDS-Describes the following trouble clearing aids:

- Alarm Log

- Error Log

- Maintenance Commands

- Facilities Access Test

- ABBREVIATIONS AND ACRONYMS

- INDEX

# **SWITCH HARDWARE**

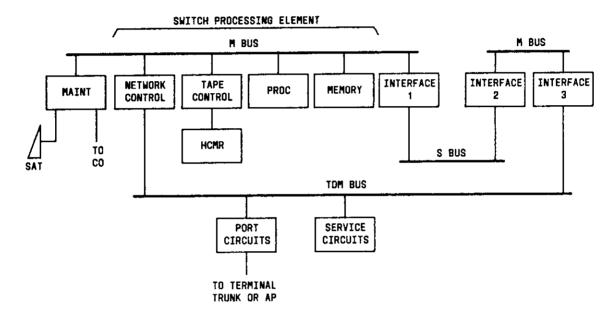

Figure 1 shows the System 75 switch. The basic switch hardware consists of the following:

- · Switching network

- Switch processing element (SPE)

- High capacity minirecorder (HCMR)

- Applications processor (AP) interface

- Maintenance circuit pack

- · Power system

Figure 1. Communications Switch

### SWITCHING NETWORK

System 75 uses distributed processing techniques to provide switched voice and data services. The switch operates at 64 Kbps. The switching network consists of the following:

- Time division multiplex (TDM) bus

- Intelligent ports

- · Service circuits

The intelligent ports connect external communications facilities to the TDM bus. The TDM bus connects the intelligent ports to the SPE through the network control circuit. The service circuits provide tone sources, receivers, detectors, and pooled modems.

### TDM Bus

# Functional Description

The TDM bus consists of two groups of eight signals (A and B buses) and five control lines with matching grounds. The port circuit packs place digitized voice [pulse code modulated (PCM)] signals on the bus. Control channel information is carried on the bus in an 8-bit Control Channel Message Set (CCMS) data signal. The CCMS data signal allows the SPE to communicate with the port circuit packs.

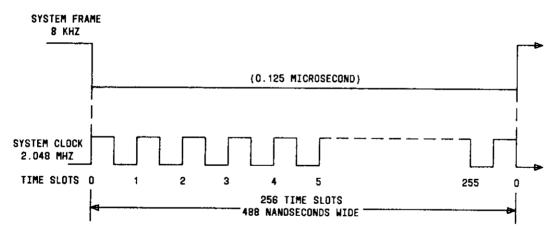

The bus operates at 2.048 MHz. The system framing pulse is 8 kHz. This provides 256 time slots on both the A and B bus. The time slots are 488 ns wide. Time slots are generated as shown in Figure 2.

Figure 2. TDM Bus Time Slot Generation

Two time slots are required for a 2-party conversation. Each party transmits (talks) on one time slot and receives (listens) on another. The initial system software limits the number on a conference call to six. During a conference connection, each member of the conference transmits on an individual time slot while receiving on as many as five other time slots.

The actual switch capacity is 236 simultaneous conversations, because some slots are reserved for system use. The first five slots on Bus A (00-04) are used for the internal control channel on which the ports talk to the SPE. Seventeen slots on the B bus are used

for system tones (see Table A). Slots 05 through 12 on the A bus and slots 256 through 260 on the B bus are reserved for future use. The last two slots on each bus (254, 255, 510, and 511) are currently not used.

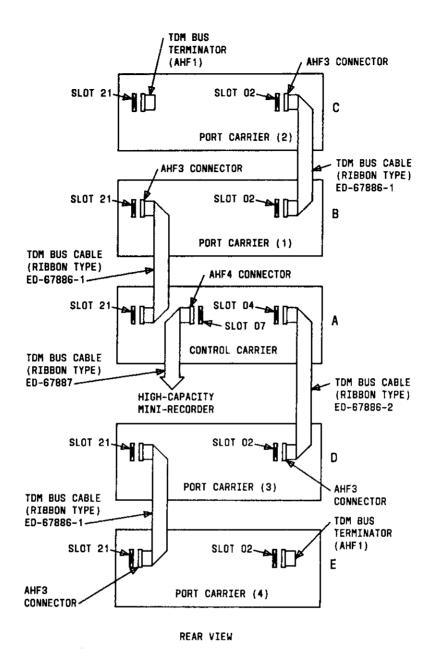

### Physical Characteristics

The TDM bus contains two identical 8-bit buses (A and B). The TDM bus snakes continuously through several carriers within the cabinet as shown in Figure 3. The total length is about 15 feet for a system with four port carriers. The bus is driven from any of the circuit pack slots in the carriers. Similarly, a signal on the bus can be received by any circuit pack.

Within a carrier, the bus is printed on one side of the backplane while the other side is solid ground. Between carriers, coax cables are used to minimize electromagnetic interference (EMI).

# **Electrical Characteristics**

The TDM bus is an unbalanced, low characteristic impedance transmission line. Paths printed over a ground plane on the carriers and the coax cables between carriers maintain this impedance level over the full length of the bus.

Each end of the bus is terminated to ground with a separate resistor for each of the 16 bits. Each circuit pack connects to the bus through a custom bus driver device. The bus driver is a switchable constant current source so that even in the "high" output state there is no bus loading to cause reflections. The current output of the drivers is adjusted so that logic "high" is 1.5 volts compared to a "low" of 0 volts.

TABLE A. Dedicated Time Slots For Tones

| TDM-B Slot No. | Tone                          |

|----------------|-------------------------------|

| 261            | 697 Hz*                       |

| 262            | 770 Hz*                       |

| 263            | 852 Hz*                       |

| 264            | 941 Hz*                       |

| 265            | 1209 Hz*                      |

| 266            | 1336 Hz*                      |

| 267            | 1447 Hz*                      |

| 268            | 1637 Hz*                      |

| 269            | Dial Tone                     |

| 270            | Re-order Tone                 |

| 271            | Intercept Tone                |

| 272            | Busy Tone                     |

| 273            | Audible Alerting Tone         |

| 274            | Special Audible Alerting Tone |

| 275            | 2025 Hz                       |

| 276            | 2225 Hz                       |

| 277            | Music                         |

<sup>\*</sup>These tones are used to generate touch-tone signals.

Figure 3. TDM Bus Wiring Diagram—Fully Loaded (4-Port Carrier and Control Carrier)

Configuration

# Intelligent Ports

# Common Circuitry

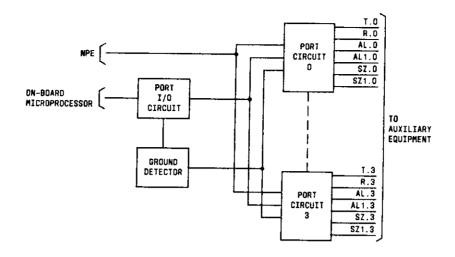

The port circuit packs provide the link between trunks or terminals and the TDM buses. Eight port circuits are provided on most port circuit pack. The MET Line, Tie Trunk, and Auxiliary Trunk circuit packs contain four port circuits.

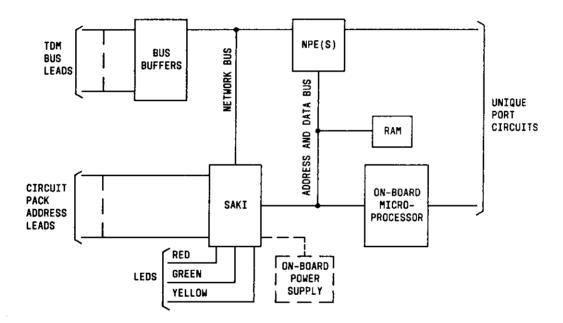

Each of the System 75 port circuit packs contain a number of common elements (see Figure 4) as well as the unique port circuits. The common elements are as follows:

- · Bus buffers

- Sanity and control interface (SAKI)

- On-board microprocessor with external random access memory (RAM)

- Network processing elements (NPEs)

Figure 4. Port Circuit Pack Common Circuitry

### **Bus Buffers**

The bus buffers are the digital interface between the backplane TDM bus wires (system bus) and the on-board circuitry (data bus). They receive or transmit on either of the two 8-bit TDM buses. They also receive and distribute clock and frame signals.

### SAKI

The SAKI is the control interface between the SPE that sends information via the network control circuit down the TDM buses and the on-board circuitry controlled by the on-board microprocessor. The SAKI receives control information (down-link messages) on the first five time slots and, as requested by the on-board microprocessor, transmits control information (up-link messages) on these same time slots.

### The SAKI also:

- Identifies the circuit pack to the SPE (location and vintage)

- Controls status indicator light-emitting diodes (LEDs)-red (failure), green (test), and yellow (circuit busy)

- Initiates power-on startup procedures

- Checks the on-board microprocessor for sanity and causes reinitialization in case of problems

- Takes NPEs out of service under control of the on-board microprocessor

- Resets the protocol handler on the Hybrid Line circuit pack and the formatter devices on the Digital Line circuit pack

- Takes the whole circuit pack out of service on command from the SPE or when it determines that on-board interference is present in the control time slots

### On-Board Microprocessor With External RAM

The on-board processor performs all low level functions such as scanning for changes and relay operations. In general, it carries out commands received from the SPE and reports status changes to it. The external RAM stores control channel information and port-related information.

### **NPEs**

Each port circuit pack contains one, two, or four NPEs. The Analog Line, Hybrid Line, CO Trunk, and DID Trunk circuit packs contain two NPEs. The Digital Line circuit pack contains four NPEs. The MET Line, Auxiliary Trunk, and Tie Trunk circuit packs contain one NPE.

The NPEs perform switching network functions for the port circuits. Under control of the on-board microprocessor, an NPE can connect a port circuit to any one of the TDM bus time slots. More specifically, it allows a port circuit to "talk" on one time slot and "listen" to the same time slot (NPE sidetone) and on up to five other time slots at the same time. In 2-wire circuits that provide their own sidetone, the NPE sidetone is not used.

# Line Ports

# Analog Line

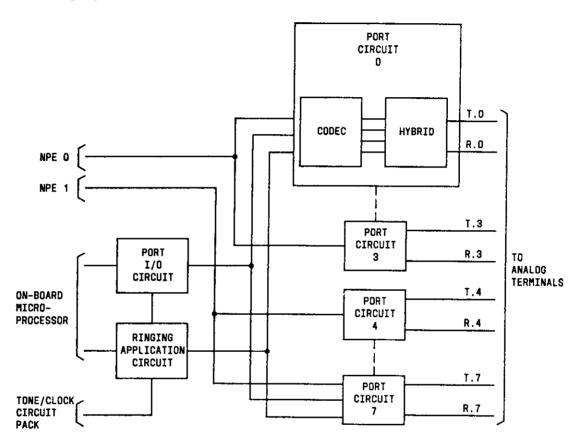

The Analog Line circuit pack provides the electrical interface between eight analog voice terminal lines and the TDM bus. Figure 5 shows the following Analog Line unique circuitry:

- Ringing application circuit

- Port input/output (I/O) circuit

- Eight port circuits

Figure 5. Unique Analog Line Circuitry

Ringing Application Circuit: This circuit receives ringing voltage from the 124B frequency generator located in the Power Distribution Unit. It monitors ringing voltage and current, generates signals to the on-board microprocessor indicating zero ringing voltage and current, and detects a terminal user lifting the receiver during ringing. This prevents the application of ringing to the port circuit when a terminal user lifts the receiver during the ringing phase. Maintenance circuitry is also included. The maintenance circuitry detects when a terminal is connected to the port circuitry and checks for faults in the ringing application circuitry.

Port I/O Circuit: This circuit consists of bus expanders for communication between the on-board microprocessor and the port circuits. It receives commands from the on-board microprocessor and distributes them to the individual port circuits. It also accesses the port circuit scan points and passes the information to the on-board microprocessor.

Port Circuits: The eight port circuits are identical. Each port circuit consists of a coder/decoder (codec), hybrid circuit, power filter, battery feed circuit, relay driver, and surge protection circuit.

The codec is a 4-wire circuit that converts the analog signal from a voice terminal to a PCM data signal. It converts an incoming PCM data signal from the NPEs to an analog signal. The hybrid circuit converts the 4-wire analog signal from the codec to a 2-wire analog signal that is connected to the analog line. Filtered power is provided for the codec and hybrid circuits.

The battery feed circuit provides talking battery to the voice terminal. It also produces a controlled dc battery feed for short and long loops, detects when a receiver is lifted, and provides the message waiting signal by periodically turning off the feed voltage.

The relay driver provides the interface between the ringing application circuit and the port circuit. It causes ringing turn on and turn off. The surge protection circuit provides lightning surge protection for the circuit pack.

### Digital Line

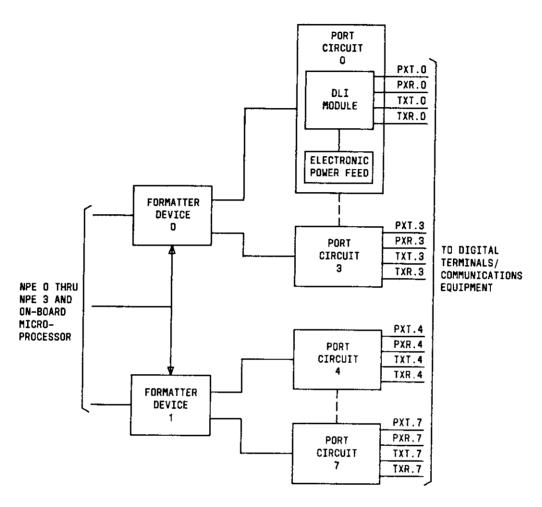

The Digital Line circuit pack provides the electrical interface between eight digital communications protocol (DCP) lines and the TDM bus. Figure 6 shows the Digital Line unique circuitry. The unique circuitry consists of two formatter devices and eight port circuits.

Figure 6. Unique Digital Line Circuitry

Formatter Devices: Each formatter device controls the format of control channel data for four DCP lines. The devices code control information from the on-board microprocessor, multiplex it with information from the NPE, and output it to the digital line interface (DLI) for transmission on the DCP line. Control information received from the DLI is stripped from the data stream, decoded, and forwarded to the on-board microprocessor.

Port Circuits: The eight port circuits are identical. Each port circuit consists of a DLI module and an electronic power feed device. The DLI module consists of a DLI device, a pair of interface devices, and two isolation transformers. The DLI device contains all functions needed to transmit and receive data over a DCP line. The transmitter function includes data

scrambling and band limit filtering. The receiver function includes equalization, clock recovery, data unscrambling, and frame detection. The two interface devices contain all discrete components (capacitors and resistors) needed to operate the DLI device correctly.

An isolation transformer is used for both the transmit and receive pair of the DCP line. Phantom power is supplied to the line (from the electronic power feed device) at the secondaries of the transformers. The primaries of the transformers connect to the DLI device.

The electronic power feed device supplies -48 volt dc phantom power to the line circuit. The electronic power feed device is a "smart" circuit breaker. When it senses an overcurrent condition, it indicates the condition on an output lead and goes into thermal shutdown if not turned off by the on-board microprocessor. When the overcurrent condition disappears, the circuit breaker can be turned on by the on-board microprocessor.

The electronic power feed device is polled regularly by the on-board microprocessor to test for overcurrent and no-current conditions. The polling can also occur upon demand.

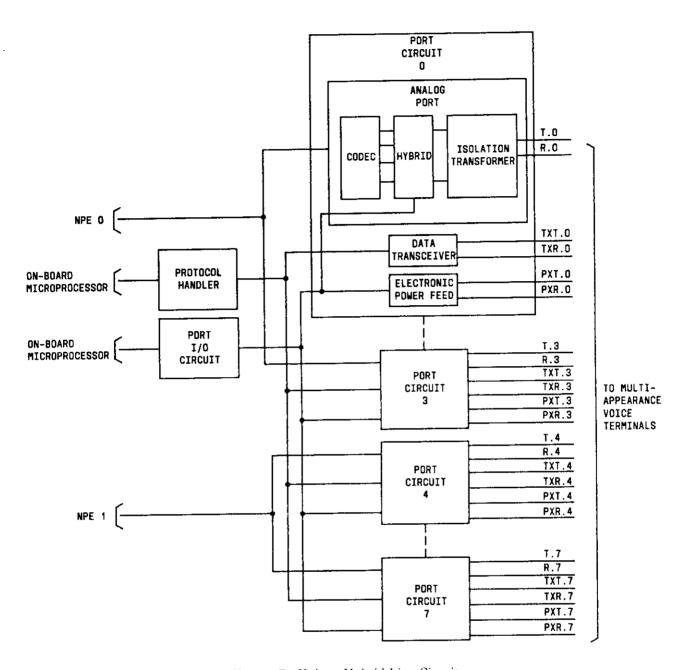

### Hybrid Line

The Hybrid Line circuit pack provides the electrical interface between eight hybrid voice terminals and the TDM bus. It terminates three pairs of wires from each terminal: analog voice pair, digital control pair, and power pair. Figure 7 shows the following Hybrid Line unique circuitry:

- · Protocol handler

- Port I/O circuit

- · Eight port circuits

**Protocol Handler:** The 8-bit on-board microprocessor translates the control information in CCMS message format to the control information message format used by the hybrid terminals. The protocol handler sends the messages to the terminals via transceivers located in the port circuits.

Port I/O Circuit: The port I/O circuit consists of a bus expander for communication between the on-board microprocessor and the port circuits. Half of the expander controls the on/off state of the electronic power feed devices located in the port circuits. The other half controls the balance in the hybrid circuit located in the analog port circuit.

Port Circuits: The eight port circuits are identical. Each port circuit consists of an analog port, one-half of a transceiver, and an electronic power feed device.

The analog port circuit consists of a codec, a hybrid circuit, an isolation transformer, and associated power filtering circuitry. The codec and hybrid circuit function the same as the codec and hybrid circuit in the Analog Line circuit pack. A lead from the port I/O to the hybrid circuit controls the terminating impedance of the hybrid circuit for testing purposes. The output of the hybrid circuit is connected to the primary of the isolation transformer. The secondary of the transformer is connected to the talking tip and ring pair with associated matching resistor.

The transceiver interfaces the control pair from the voice terminal to the protocol handler. The electronic power feed device provides -48 volts dc on the power pair to the voice terminal. The -48 volt dc input to the device is received through a fuse on the circuit pack. The device is polled by the on-board microprocessor, periodically and on demand, to test for an overcurrent and/or no-current condition. The on/off state of the device is controlled by the on-board microprocessor through the port I/O circuit.

Figure 7. Unique Hybrid Line Circuitry

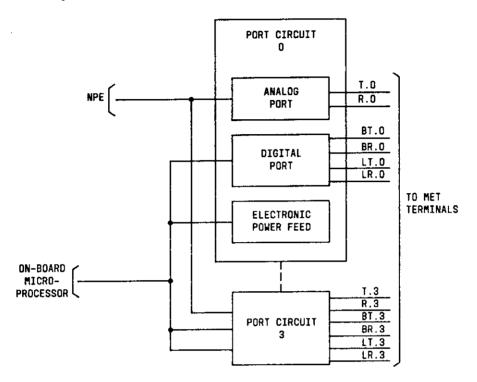

The MET line provides the interface between four multibutton electronic telephone (MET) lines and the TDM bus. Figure 8 shows the MET line unique circuitry. The unique circuitry consists of four port circuits.

Figure 8. Unique MET Line Circuitry

Port Circuits: The four port circuits are identical. Each port circuit consists of an analog port, a digital port, and an electronic power feed device.

The analog port circuit consists of a codec, a hybrid circuit, an electronic battery feed, and a power filter. The codec, hybrid circuit, and power filter function the same as in the Analog Line circuit pack. The electronic battery feed provides talking battery to the MET set. The electronic battery feed produces a controlled dc hattery feed current for short and long loops and detects when a MET set user lifts a receiver.

The digital port circuit provides a full duplex channel over two 2-wire pairs. All outgoing lamp and incoming button depression information is carried on these channels. Ringing and detection of when a MET set user lifts a receiver information is also sent over these channels.

The electronic power feed device provides phantomed -48 volt do power for the MET terminals over the data channels. The electronic power feed device is a "smart" circuit breaker. When it senses an overcurrent condition, it indicates the condition on an output lead and goes into thermal shutdown if not turned off by the on-board microprocessor. When the overcurrent condition disappears, the circuit breaker can be turned on by the on-board microprocessor.

# Trunk Ports

### CO Trunk

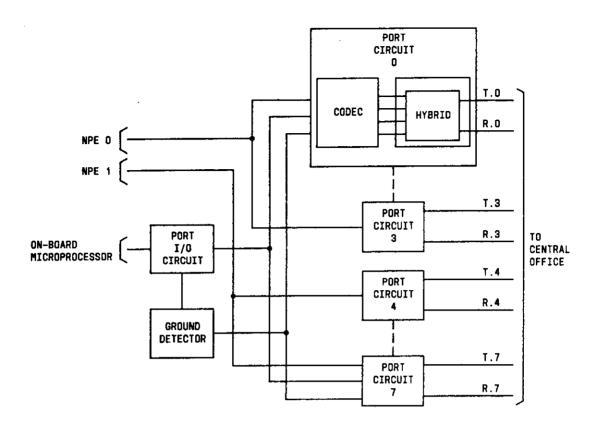

The CO Trunk circuit pack provides the electrical interface between eight central office trunks and the TDM bus. Figure 9 shows the following CO Trunk unique circuitry:

- · Ground detector circuit

- Port input/output (I/O) circuit

- · Eight port circuits

Ground Detector Circuit: The ground detector circuit determines whether ground has been applied to the tip lead (incoming or outgoing seizure). One ground sensor is used for each port circuit. Input for the ground sensor comes from the port circuit as an analog current to the -48 volt dc supply. The ground sensor's output is a port control point to the port I/O circuit.

Port I/O Circuit: This circuit functions the same as in the Analog Line port I/O circuit.

Port Circuits: The eight port circuits are identical. Each port circuit consists of a codec, hybrid circuit, line transformer, power filter, relay driver, and surge protection circuit.

The codec is a 4-wire circuit that converts an incoming PCM data signal from a system user (via the NPEs) to an analog signal. It converts the analog signal from a central office trunk to a PCM data signal. The hybrid circuit converts the 4-wire analog signal from the codec to a 2-wire analog signal that is connected to the central office trunk by the line transformer. Filtered power is provided for the codec and hybrid circuits.

The relay driver buffers and inverts the relay drive signals from the port I/O circuit so that a logic high input operates the appropriate relay. The relays control circuitry that provides the proper interfaces for ground start or loop start trunks and rotary or touch-tone dialing. The surge protection circuit provides lightning surge protection for the circuit pack.

Figure 9. Unique CO Trunk Circuitry

### DID Trunk

The DID Trunk circuit pack provides the electrical interface between eight central office trunks arranged for direct inward dialing (DID) and the TDM bus. Figure 10 shows the DID Trunk unique circuitry. The unique circuitry consists of a port input/output (I/O) circuit and eight port circuits.

Port I/O Circuit: This circuit functions the same as in the Analog Line port I/O circuit.

Port Circuits: The eight port circuits are identical. Each port circuit consists of a codec, balance network, trunk interface unit, loop termination circuit, and power filter.

The codec is a 4-wire circuit that converts the analog signal from a DID trunk to a PCM data signal. The codec converts an incoming PCM data signal from the NPEs to an analog signal.

The trunk interface unit contains a hybrid, a 2-wire interface circuit, and control circuitry. The hybrid circuit converts the 4-wire analog signal from the codec to a 2-wire analog signal that is connected to the analog line by the 2-wire interface circuit. The control circuitry controls loop current, internal signal gain, terminating resistance, battery feed shutdown, and battery reversal.

The loop termination circuit provides a fixed impedance to the DID trunk. Filtered power is provided for the codec and hybrid circuits.

Figure 10. Unique DID Trunk Circuitry

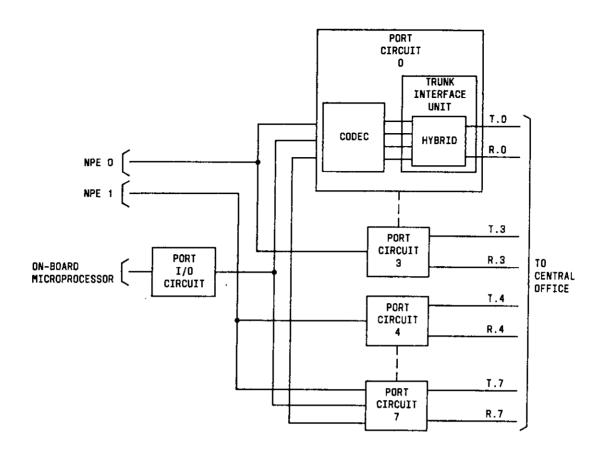

### Tie Trunk

The Tie Trunk circuit pack provides the electrical interface between four 6-wire tie trunks and the TDM bus. Two tip and ring pairs form a 4-wire analog transmission line. The E and M pair are used for signaling. The T and R pair transmit analog signals from the circuit pack. The T1 and R1 pair receive analog signals from the tie trunk. The E and M pair are dc signaling leads used for call setup handshaking. The E lead receives signals from the tie trunk and the M lead provides signals from the circuit pack. Figure 11 shows the following Tie Trunk unique circuitry:

- · Ground detector circuit

- Port I/O circuit

- . Four port circuits

Ground Detector Circuit: This circuit determines if a ground has been applied to the E lead. Ground detector inputs come from the port circuits as an analog current to the -48 volt dc supply. Its output is a port control point to the port I/O circuit.

Port I/O Circuit: This circuit functions the same as in the Analog Line port I/O circuit.

Port Circuits: The port circuits are identical, except for port 3 where part of the E-lead maintenance circuit is located. Each port circuit consists of a codec with associated input and output line transformers, analog operational amplifiers, a power filter, loop-around transistors, port control comparators, a relay driver, an electronic power feed device, an E-lead test maintenance circuit, and surge protection circuits.

The codec converts the incoming 4-wire analog signal from the tie trunk to a PCM data signal. The codec converts the incoming PCM data signal from the NPE to an analog signal. Outgoing and incoming line transformers provide dc isolation to the tip and ring leads. Analog operational amplifiers provide amplification and buffering for the codec and network and loop-around gain compensation. Filtered power is provided to the codec and amplifiers.

The loop-around transistors are under control of the port control comparators and provide a loop-around path for the analog signal for testing purposes. The relay driver buffers and inverts the relay drive signals from the port I/O circuit so that a logic high input operates the appropriate relay. The relays and electronic power feed device control the M-lead circuitry to provide the proper signaling handshake for call progress trunks and rotary dialing.

The electronic feed device provides a -48 volt dc current to the M-lead circuits. It also tests the M-lead circuits for opens or shorts and prevents uncontrolled operation during power-up. The E-lead test circuit provides a ground to the ground detector circuit for testing purposes. The surge protection circuitry provides lightning surge and power cross protection for the circuit pack.

Figure 11. Unique Tie Trunk Circuitry

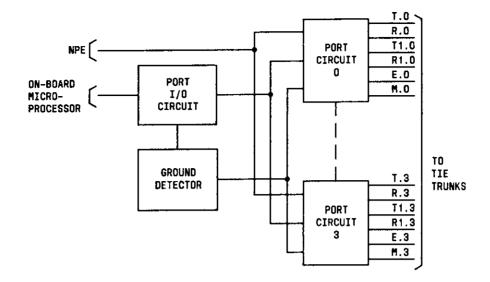

### Auxiliary Trunk

The Auxiliary Trunk circuit pack provides the electrical interface between four ports provided for client-provided equipment (CPE) and the TDM bus. It is connected to the CPE by up to three pairs of wires. The transmission pair (T and R) carry voice signals and touch-tone control signals. T and R also provide a loop start seizure indication to the CPE. The seizure pair (SZ and SZ1) provide seizure indication to the CPE. The signal pair (S and S1) provide answer supervision and/or make-busy information from the CPE. Depending on the application, the transmission pair only or all three pairs are connected to the CPE.

Figure 12 shows the following Auxiliary Trunk unique circuitry:

- · Ground detector circuit

- Port input/output (I/O) circuit

- · Four port circuits

Ground Detector Circuit: This circuit determines if an answer-supervision or make-busy signal from the CPE is present. The ground detector's inputs come from the port circuits as an analog current to the -48 volt dc supply. Its output is a port control point to the port I/O circuit.

Port I/O Circuit: This circuit functions the same as in the Analog Line port I/O circuit.

Port Circuits: The four port circuits are identical. Each port circuit consists of a codec, hybrid circuit, line transformer, power filter, relay driver, battery polarity sensor, and surge protection circuit.

The codec is a 4-wire circuit that converts the analog signal from the CPE to a PCM data signal. It converts an incoming PCM data signal from the NPE to an analog signal. The hybrid circuit converts the 4-wire analog signal from the codec to a 2-wire analog signal that is connected to the CPE by a line transformer. Filtered power is provided for the codec and hybrid circuits.

The relay driver buffers and inverts the relay drive signals from the port I/O circuit so that a logic high input operates the appropriate relay. The relays control circuitry that provide the proper interfaces for CPE and rotary dialing.

The surge protection circuit provides metallic lightning surge protection for the circuit pack. Longitudinal surges are isolated from the hybrid and codec by the line transformer.

Figure 12. Unique Auxiliary Trunk Circuitry

### Service Circuits

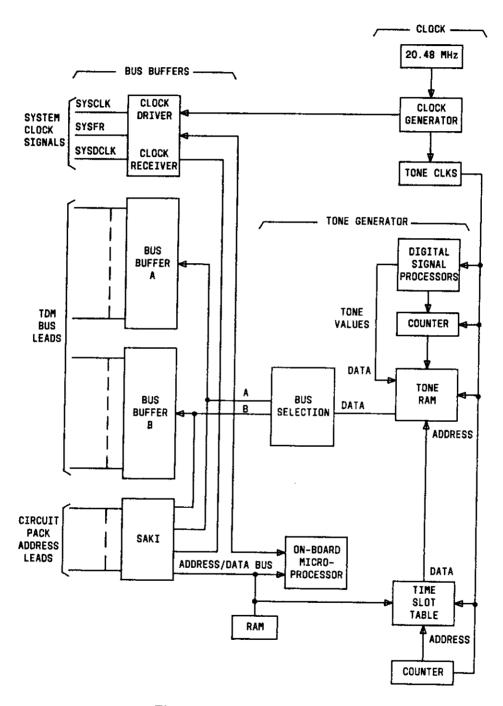

### Tone/Clock

The Tone/Clock circuit pack provides clock signals to run the system and system call tones. The Tone/Clock circuit pack consists of the following (see Figure 13):

- · Bus buffers

- Sanity and control interface (SAKI)

- On-board microprocessor with external RAM

- · Clock circuit

- Tone Generator

- Time slot table and counter

Each system contains one Tone/Clock circuit pack. Power for the circuit pack (+5 volts dc) is provided on the backplane.

Bus Buffers: There are three bus buffers on the Tone/Clock circuit pack. The clock driver/receiver interfaces the three system clock signals (2.048 MHz, 8 kHz, and 160 kHz) to the TDM bus. Bus buffer A interfaces messages to and from the SPE on TDM bus A to the Tone/Clock circuit pack. Bus buffer B interfaces the system tones (see Table A) from the circuit pack to TDM bus B. Music is not produced by the Tone/Clock circuit pack. Music is provided by CPE through the Auxiliary Trunk circuit pack.

These tones are programmed to be placed on bus A when the circuit pack is first powered up. A downlink message from the SPE causes the tones to be switched to bus B.

**SAKI:** This circuit functions the same as in the SAKI in the common circuitry for the intelligent port circuits.

On-Board Microprocessor With External RAM: This circuit functions the same as the microprocessor in the common circuitry for the intelligent port circuits. In addition, it tells the dual-port RAM in the time slot table circuit the appropriate time slots to place the tones. The external RAM also has work space for complex tones.

Clock Circuit: The clock circuit consists of a 20.48-MHz oscillator, a clock generator, and a tone clock. The clock circuit runs independent from the rest of the Tone/Clock circuitry. The clock circuits start running when the circuit pack is first powered up and is not controlled by the on-board microprocessor.

The output of the 20.48-MHz oscillator is fed to the clock generator. The clock generator contains circuits that divide by 10, 2560, and 128. These circuits produce the 2.048-MHz, 8-kHz, and 160-kHz clock signals, respectively. The clock generator feeds these signals to the clock driver/receiver bus buffer and the tone clock. The tone clock uses these signals to synchronize the counters in the tone generator and time slot table circuits to the TDM bus.

Tone Generator: The tone generator consists of two digital signal processors (DSPs), a counter, and a dual-port tone RAM. The DSPs operate at 8 MHz and produces 32 different tones. The dual-port tone RAM stores these tones in 32 different addresses. The counter under control of the tone clock causes the DSPs to transmit one sample of each tone every 8-kHz. The counter is synchronized to the TDM bus and is offset to provide delay needed for access time.

Time Slot Table: The time slot table consists of a dual-port time slot table RAM and a counter. The dual-port RAM contains 256 different addresses. These addresses correspond to the time slots on TDM bus B. The counter sequences through the time slot table addresses in the dual-port RAM and causes the proper tone(s) to be output by the dual-port tone RAM on TDM bus B time slots.

Figure 13. Tone/Clock Circuit

### Tone Detector

The Tone Detector circuit pack provides four touch-tone receivers and two general purpose tone receivers that detect the appropriate system and network tones on the TDM bus.

The Tone Detector circuit pack consists of the same common circuitry as the intelligent port circuits and the following unique circuits (see Figure 14):

- Port I/O circuit

- . Port or DSP Sanity check circuit

- · Eight port circuits

Common Circuitry: The Tone Detector circuit pack common circuitry functions the same as the port circuits common circuitry.

Port I/O and Sanity Check Circuit: This circuit interfaces the on-board microprocessor to the port circuits and checks the sanity status of the port circuits' DSPs.

Port Circuits: There are eight port circuits. Each port circuit is connected to a network processing element (NPE) serial input and serial output. Port circuits 0, 1, 4, and 5 are touch-tone ports. Port circuits 2 and 4 are general purpose tone detector ports. Each of the six port circuits has an associated DSP. The remaining port circuits (3 and 7) provide a loop-around path for testing purposes and are tied directly with no associated circuitry to an NPE.

The two general purpose tone detector port circuits are identical and detect the following:

- · Call-progress tones

- · Modem answer-back tones

- · Transmission test tones

- Noise

The four touch-tone tone detector port circuits are also identical. They detect touch-tone signals required for proper signaling.

The six port circuits used for tone detection contain a DSP, NPE to DSP interface circuitry, and a DSP restart circuit. The touch-tone port circuit also contains an interrupt filter. The general purpose tone detector port circuit will support an add-on emulator circuit for future changes in its DSP operating program.

TDM bus signals are connected to the DSP in serial form from the NPEs by the DSP interface circuit. Serial clock and data signals connect directly from the NPE to the DSP. The system framing signal is synchronized and connects to the DSP.

The DSP restart circuit controls the DSPs. When the on-board microprocessor is not functioning properly, the DSP restart circuit takes all of the DSPs out of service. It restarts each individual DSP under control of the port I/O and sanity check circuit. It resets the general purpose tone detector DSP after each use.

The two types of DSPs (general purpose tone detector and touch-tone) differ in internal programming and running speed. The touch-tone DSPs, under control of the on-board microprocessor, write data synchronously to the NPEs. The interrupt filter detects valid touch-tone signals and allows end-to-end transmission while blocking end-to-end touch-tone signaling. The general purpose tone detector DSPs, under control of the on-board microprocessor, write data asynchronously to the NPEs.

Figure 14. Tone Detector Circuit

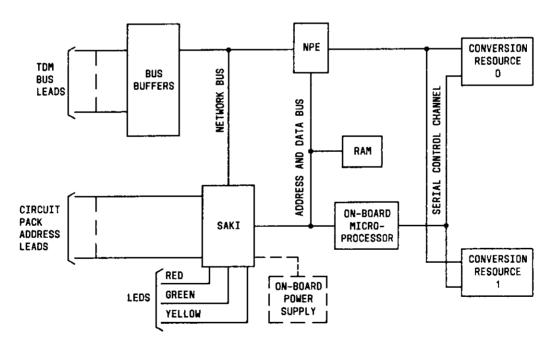

### Pooled Modem

The Pooled Modem circuit pack supports 0-300 and 1200 bits per second (bps) data speeds and provides the following:

- Circuitry to convert a DCP, Mode 2 signal into a signal compatible with the modulation formats of the 212-series modems

- Modem emulation (See below)

| 0-300 Asynchronous 300 Asynchronous 1200 Asynchronous 1200 Synchronous 1200 Synchronous |

|-----------------------------------------------------------------------------------------|

• Several modem functions appropriate to 212-series modem operations

A maximum of 16 Pooled Modem circuit packs are allowed in a system.

The Pooled Modem circuit pack consists of common circuitry and two conversion resources (see Figure 15). The conversion resource (port) enables two dissimilar devices to talk to each other. Each port has two connections to the TDM bus. One connection is made to a remote data module, DCP Mode 2 format. The other connection is made to a remote mode, PCM signal.

Figure 15. Pooled Modem Circuit

Common Circuitry: The Pooled Modem common circuitry provides the same general function as the intelligent port common circuitry.

Conversion Resources: The two conversion resources (port circuits) are identical and each contain the following:

- Microprocessor

- Transmit and receive I-channel controller (TRIC)

- Universal synchronous/asynchronous receiver and transmitter (USART)

- Data USART clock (DUCK)

- DSP

The port circuit microprocessor enables communications between a remote data module and a remote modem through control of an on-board data module and modem. The port circuit microprocessor communicates with the on-board microprocessor over a serial control channel. This channel allows the on-board microprocessor to send messages to the port circuit microprocessor that specify call startup information, option settings, information requests, various test modes, and call termination information. It also allows the port circuit microprocessor to inform the on-board microprocessor of various port circuit status information.

The DUCK and TRIC interface the I-channel information between the port circuit and the remote data module. The port circuit microprocessor controls the operation of the DUCK and the TRIC by appropriately programming their internal registers. The DUCK and TRIC together recreate the clock and serial data stream from the remote data module, and process an on-board clock and serial data stream for delivery to the remote data module. Control information (handshaking and RS232 control leads) is passed between the port circuit microprocessor and the remote data module by the TRIC.

The USART interfaces the DUCK's serial data stream to the port circuit microprocessor. The USART can be programmed by the port circuit microprocessor to operate synchronously or asynchronously. The USART also performs the following tasks for the port circuit microprocessor:

- Appends start and stop bits to parallel data received from the port circuit microprocessor in the asynchronous mode

- Converts serial data received from the port circuit microprocessor to parallel data and converts serial data received from the DUCK to parallel data

- · Double buffers data in both directions

- · Detects and generates break characters

The DSP provides modem emulation. It interfaces the port circuit PCM signal and the remote modem. PCM samples are communicated between the DSP and an analog line or trunk circuit connected directly or indirectly to the remote modem. The port circuit microprocessor directs the DSP to execute one of many programs. The DSP produces data, carrier detection, and timing information for the port circuit microprocessor. It accepts data and timing information from the port circuit microprocessor in a format dependent on its operating mode.

# SWITCH PROCESSING ELEMENT

The main components of the switch processing element (SPE) are as follows (see Figure 1).

- Network Control

- Processor

- Memory

- . Tape Control

These four components are interconnected by the 16-bit, 2-MHz M (memory) bus located on the backplane. The M bus also contains 24 address, 5 parity, and 10 interrupt and control lines.

The Maintenance circuit pack is associated with the SPE on the same M bus. The AP interface circuit packs are also associated with the SPE via the M bus, the S (system) bus, and an identical but shorter M bus.

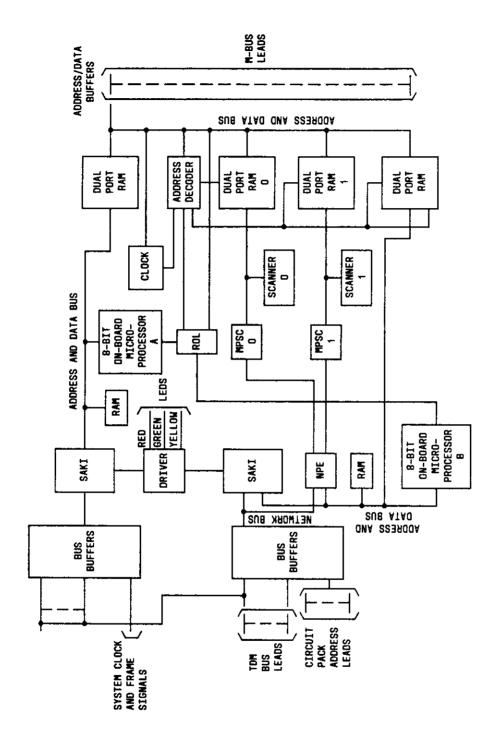

#### **Network Control**

The Network Control circuit pack functions as follows:

- Synchronizes control channel messages between the switch processing element (SPE) over the M bus and the port circuits over the TDM bus

- Provides switched data access to the SPE for system administration, station message detail recording (SMDR), and switch maintenance

- · Provides the time, day, and month to the SPE with battery holdover

- · Monitors system clocks

Each system contains one Network Control circuit pack. Power for the circuit pack (+5 volts dc) is provided on the backplane.

The Network Control circuit pack consists of the following circuitry (see Figure 16):

- 8-bit on-board microprocessor A with external RAM and associated network interface circuitry

- 8-bit on-board microprocessor B with external RAM and associated network interface circuitry

- · Two scanner circuits

- · Clock circuit

- M bus interface circuit

Figure 16. Network Control Circuit

# 8-Bit On-Board Microprocessor A With External RAM

The 8-bit on-board microprocessor A acts as a switch passing messages back and forth between the SPE and the on-board microprocessors located in the port circuits. It is the focal point for all uplink messages from the port circuits as well as the central distribution point for all downlink control messages. It continuously scans, over the TDM bus, the port circuit microprocessors for sanity and activity.

The 8-bit on-board microprocessor A also keeps track of the status of the three system clocks on both a combined and individual basis. As part of the restart sequence, the microprocessor must clear the clock after an interrupt and after a clock failure is detected. The external RAM stores control channel information and port related information.

The network interface circuitry for the 8-bit on-board microprocessor A consists of bus buffers and a SAKI. The bus buffers provide the interface between the TDM bus and the on-board data buses to the SAKI. The SAKI receives and transmits control messages on the first five time slots on the TDM bus A. It also controls the LEDs on the front of the circuit pack through a driver circuit. The 8-bit on-board microprocessor A communicates with the SAKI and external RAM over an address and data bus.

# 8-Bit On-Board Microprocessor B With External RAM

The 8-bit on-board microprocessor B provides the intelligence to communicate control information back and forth to the SPE through the 8-bit on-board microprocessor A. This microprocessor differs from the port circuit microprocessors in that it also has access to the SPE through a dual port RAM. This enables a distinct control driver to respond to call processing messages and to control the four DCP data channels provided by the scanner circuits.

The 8-bit on-board microprocessor B processes maintenance messages, network updates, downlink acknowledgments, and uplink requests received from the 8-bit on-board microprocessor A. All other messages are passed directly to and from the SPE through the dual-port RAM. The external RAM stores control channel information and port-related information.

The network interface circuitry for the 8-bit on-board microprocessor B consists of bus buffers, an NPE, and a SAKI. The bus buffers interface the TDM bus and the on-board data buses to the SAKI and the NPE.

The NPE serves as a switching network for the four DCP data channels provided by the scanner circuits by picking digital data from the correct time slot. It receives and transmits data to and from the scanner circuits. The network side of the NPE receives and transmits these data signals in parallel on the TDM bus. NPE operation is controlled by the 8-bit on-board microprocessor B over the address and data bus.

The SAKI transmits and receives control messages to and from the TDM bus. It is controlled by the on-board 8-bit microprocessor B in the same manner as the NPE. Under certain circumstances, such as the absence of polling by the SPE or detection of unexpected signals on the control time slots, it can reset the on-board 8-bit microprocessor B. When the SAKI receives a control message, it interrupts the on-board 8-bit microprocessor B to read the existing message before a new one arrives.

#### Scanner Circuits

The Network Control circuit pack contains two identical scanner circuits. It consists of a multi-programmable serial controller (MPSC) and a scanner. The MPSC is a sophisticated USART device that provides high level support for the scanner. The scanner transfers information between the MPSC (receiving data from the NPE serial channels) and dual-port RAMs (receiving data from the SPE) based on MPSC status and dual-port RAM pointers. Each scanner services two channels per MPSC with one dual-port RAM split between two channels.

The scanner processes data, EIA, and handshake packets and moves the contents to the proper location in the buffer shared with the SPE. For transmitting, the scanner performs baud rate emulation as it builds packets with data downloaded from the SPE.

### Clock Circuit

The clock circuit consists of a timer, a battery, and an inverter. The timer is a single-chip, time-of-day clock. It indicates to the SPE the current time, day, and month. The lithium battery is a 3-volt supply used to back up the timer if system power is lost for extended periods of time. The inverter circuit properly operates the timer during battery backup.

#### M Bus Interface Circuit

The M bus interface circuit provides a communication interface with the SPE for the 8-bit on-board microprocessors A and B and the scanner processors. It consists of an address decoder circuit, a readable output latch (ROL) circuit, four dual-port RAMS and address/data buffers.

The address decoder circuit decodes address information that appears on the M bus with command signals. These command signals access the real-time clock, reset the 8-bit on-board microprocessor A and data channels, and operate the ROL circuit.

The ROL circuit is a control register and is readable and writable from the M bus. The ROL circuit allows the SPE to control the 8-bit on-board microprocessors A and B and provides an indication of clock failure.

The four dual-port RAMs provide the proper interface for each of the individual processors. The two dual port RAMs that interface the scanners to the SPE are identical. Each dual port RAM stores 512 eight-bit bytes.

The address/data buffers interface the Network Control circuit pack with the M bus address and data lines. The address lines from the M bus can drive up to two on-board devices. Address lines that are needed by more than two devices are buffered. The 16-bit wide M bus interfaces 8-bit wide memory components on the Network Control circuit pack. The correct bus buffer is selected according to the state of inputs to the address decoder circuit and the dual-port RAMS.

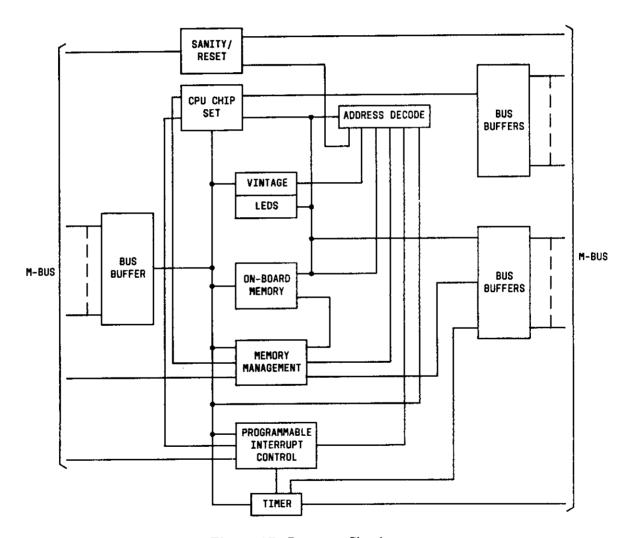

#### Processor

The Processor circuit pack is the general purpose vehicle that supports the System 75 multiuser, multiprocessor environment. Each system contains one Processor circuit pack. Power for the circuit pack (+5 volts dc) is provided on the backplane.

The Processor circuit pack consists of the following (see Figure 17):

- Central processing unit (CPU) and support circuitry

- Memory management circuit

- . On-board memory

- · On-board peripherals

- · Bus buffers

Figure 17. Processor Circuit

CPU and Support Circuitry: The CPU and support circuitry consist of the following:

- · CPU Chip Set

- · Sanity/Reset Circuit

- · Address Decode Circuit

### CPU Chip Set

The CPU chip set includes a 16-bit microprocessor and clock generation and bus control logic. The CPU executes stored programs to effect call processing or data processing functions. It provides the basic high-level control over the system.

## Sanity/Reset Circuit

The sanity/reset circuit provides system reset functions. Sanity control is provided by a watchdog timer circuit that is triggered periodically by the CPU. A reset stimulus can originate from a power up of the Processor circuit pack, the Maintenance circuit pack, the Network Control circuit pack, or a CPU sanity timeout.

#### Address Decode Circuit

Each on-board peripheral is assigned a unique address in I/O space to allow independent CPU control. In addition, each set of on-board memory devices is assigned a range of memory space addresses. The decoding circuitry translates on-board addresses into individual device select signals.

Memory Management Circuitry: The memory management circuitry supports a high level multiprocess software environment. The bootstrap program in erasable programmable read-only memory (EPROM) sets up an initial environment and enables the memory management circuitry. The memory management circuitry consists of the following:

- · Segment descriptor RAM

- Memory management control circuit

- Address arithmetic and logic unit (ALU)

- Address comparator

- · Exception logic circuit

A set of 16 segment descriptors contained in RAM controls access to all of main memory (Memory circuit pack) on the M bus. The memory management control circuit provides the status of the memory management circuit to the CPU and allows the memory management circuit to be enabled by bootstrap or diagnostic programs.

The virtual addresses produced by the CPU are translated into a physical M bus address by the ALU. The address comparator checks that the virtual addresses are valid.

The exception logic circuit detects memory management circuit commands that cannot be executed and certain hardware faults. It logically combines the exceptions and faults to create a non-maskable interrupt (NMI) to the CPU. The cause of the NMI is latched and made available to the CPU to allow recovery from the fault.

On-Board Memory: The on-board memory consists of read-only memory (ROM) and RAM. This memory does not store any applications related software. The ROM contains the bootstrap and low-level diagnostic programs.

On-board Peripherals: The Processor circuit pack on-board peripherals consist of the following:

- · Vintage straps and LEDs

- Programmable interrupt controller (PIC)

- Timer

## Vintage Straps and LEDs

Four vintage straps identify circuit pack hardware vintage to the CPU. The three LEDs indicate CPU status—red (failure), green (test), and yellow (busy).

#### PIC

The PIC logically combines the eight sources of maskable interrupt to a single interrupt to the CPU. In addition, the PIC provides priority arbitration and masks each source independently. Four of the interrupts are from off-board sources and four are from the on-board timer.

#### Timer

The timer provides five programmable timer channels. Four of the channels are connected as maskable interrupts to the PIC. The fifth output is connected to the M bus for S bus access.

Bus Buffers: The bus buffers interface all data, address, and command lines to the M bus. Some CPU status signals are also buffered. This isolates the circuit pack from the M bus and allows for other access to the M bus.

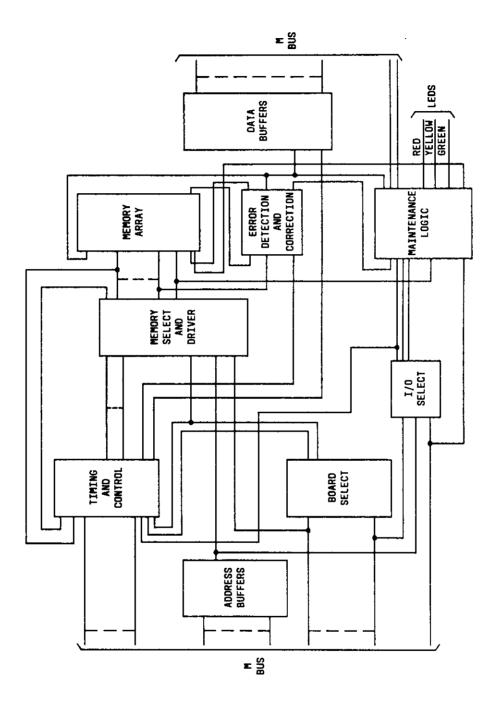

#### Memory

The Memory circuit pack provides a medium for storage and execution of the software associated with system operation. This software includes the operating system, call processing, system data, system translations, and other related programs.

Each system contains one Memory circuit pack. Power for the circuit pack (+5 volts dc) is provided on the backplane.

The Memory circuit pack (See Figure 18) consists of the following:

- Address and data buffers

- Board and I/O select logic circuit

- · Memory array

- Memory select and driver

- Error detection and correction logic circuit

- Timing and control logic circuit

- Maintenance logic

Ť,

Figure 18. Memory Circuit

Address and Data Buffers: The address and data buffers interface the Memory circuit pack to the address and data lines on the M bus.

Board and I/O Select Logic Circuit: The board and I/O select logic circuit prevents improper accessing of the Memory circuit pack. It uses the upper seven address lines and the four memory identification and processor identification address lines on the M bus.

Memory Array: The memory array consists of eighty-eight 256K dynamic RAM devices. These devices are configured in an arrangement of four 22-bit wide banks. Valid memory data is 16 bits wide. The remaining 6 bits are dedicated to check bit storage.

Memory Select and Driver: The memory select and driver selects and drives the appropriate bank of RAM in the memory array. It can force a refresh during heavy access times, determine which bank of RAM has been selected, and multiplex the memory array addresses.

Error Detection and Correction Logic Circuit: The error detection and correction logic circuit generates and latches check bits associated with each word during a memory write. These check bits are also used to check data on memory reads. The error detection and correction logic performs single bit correction and multiple bit correction.

Timing and Control Logic Circuit: The timing and control logic circuit establishes the basic memory refresh rate, memory cycle time, and error detection and correction timing. It also arbitrates conflicting memory cycles (refresh requests, M bus requests, and S bus requests). Design of the timing and control logic circuit allows two modes of memory access, traditional request and advanced start request.

A traditional request is started by memory commands from the processor or peripheral processor via the board select logic circuit. This type of memory access allows the local processor or peripheral processor to access the Memory circuit pack when there is an active refresh cycle taking place at the time of the request.

An advanced start request is started by an address latch strobe. This type of memory access allows for shorter memory access time. This is accomplished by presetting the request logic circuit and performing arbitration functions in advance of the actual memory access.

Maintenance Logic Circuit: The maintenance logic circuit provides several programmable optional modes of operation. These modes allow for testing and continued operation during certain failure conditions. The maintenance logic circuit also controls the three LEDs on the front of the circuit pack—red (failure), green (test), and yellow (busy).

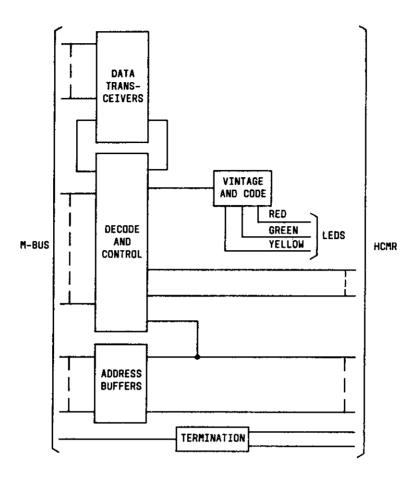

### Tape Control

The Tape Control circuit pack interfaces the high capacity minirecorder (HCMR) to the M bus. The interface provides control and data transfer between the M bus and the HCMR. The Tape Control circuit pack (see Figure 19) consists of the following:

- Decode and control circuit

- Data transceivers

- · Address buffers

- · Vintage and code circuit

- Termination circuit

The decode and control circuit is a logic array that maps address and command signals on the M bus into device select and timing signals required to interface the HCMR. The data transceivers provide a bidirectional transmission path between the M bus and the HCMR. The address buffers buffer the address lines from the M bus to the HCMR and use the decode and control circuit to generate a translation of interface commands for the HCMR. The vintage and code circuit indicates circuit pack vintage to the SPE and provides circuit pack status on the faceplate LEDs—red (failure), green (test), and yellow (circuit busy). The termination circuit includes a current programming resistor that controls the current limit on the circuit pack and provides terminations for unused HCMR signals.

Figure 19. Tape Control Circuit

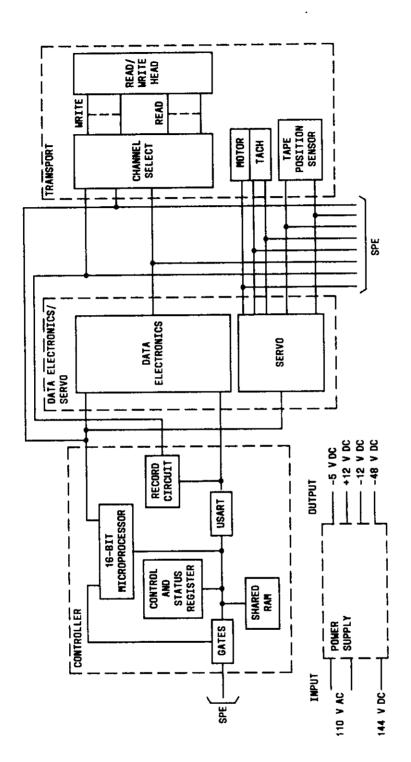

## HIGH CAPACITY MINIRECORDER

### General

The high capacity minirecorder (HCMR) provides a nonvolatile system bootstrap and translation storage device. The HCMR uses the incremental operating mode. In the incremental mode, data is efficiently read or written one single block of data at a time. The HCMR tape cartridge stores up to 12M bytes of data in the incremental mode.

### Tape Cartridge

Data is written sequentially, a block at a time, on each of the five tracks on the tape cartridge. The tracks are arranged in serpentine fashion. Subsequent access, for reading or editing, can be done randomly over the blocks previously written.

The high density digital tape in the cartridge is 600 feet (183 m) long. During read or write operations, the tape speed is 50 inches (127 cm) per second. During search operations, the tape speed is 100 inches (254 cm) per minute.

# High Capacity Minirecorder Circuit Packs

The HCMR contains four circuit packs (see Figure 20) housed in an apparatus mounting located in the power distribution unit. The four circuit packs are as follows:

- Controller

- Data Electronics/Servo

- Transport

- Power Supply

Figure 20. High Capacity Minirecorder Circuit

The circuit packs in the HCMR are interconnected by a bus on the backplane of the apparatus mounting. The Controller, Data Electronics/Servo, and Transport circuit packs have three LEDs on the faceplates—red (failure), green (test), and yellow (in-use). These three circuit packs also have an 8-bit vintage register that can be read by the Controller and reported to the SPE.

The Power Supply circuit pack has two green LEDs. When the upper LED is dark, input power is not present. When the lower LED is dark, output voltages are not within tolerances.

#### Controller

The Controller circuit pack main component is a 16-bit microprocessor. Programs executed by this microprocessor generate the data block format, select the tape direction and speed, control the read/write electronics, and monitor the other HCMR circuit packs.

The interface to the SPE via the Tape/Control circuit pack is via the shared RAM and the hardware command and status registers. The shared RAM buffers one block of data and passes commands and status between the Controller circuit pack and the SPE.

A high speed USART does the parallel-to-serial data conversion when writing on tape and the serial-to-parallel to serial conversion when reading from tape. This same USART also does a cyclic redundancy check (CRC) for each frame of data.

The record circuitry digitally encodes the output of the USART for transmission to the Transport circuit pack. The bit stream is precompensated for peak shift.

## Data Electronics/Servo

The data electronics portion of this circuit pack performs the read function. It interfaces the single digital channel on the Controller circuit pack to the selected read head analog output in the Transport circuit pack.

The servo controls the dc motor on the Tape Transport circuit pack. Servo control logic is contained in an 8-bit microprocessor. The servo responds to one of five velocity commands from the Controller circuit pack—stop, normal speed forward or reverse, and search speed forward or reverse.

#### Tape Transport

The Tape Transport circuit pack contains the 5-track read/write head and a permanent magnet dc motor with tachometer. It also contains an optical sensor that responds to the punched holes in the tape to provide the basic information used by the Controller circuit pack to determine the beginning and end of tape, load point, and early warning positions. Mechanical sensors indicate when the cartridge is in place and show the write protect status.

# Power Supply

The Power Supply circuit pack supplies the following voltages to the HCMR circuit packs.

| Tolerance |

|-----------|

| 5%        |

| 5%        |

| 5%        |

| 13%       |

|           |

Input power is 110 volts ac or 140 volts dc for battery backup.

#### APPLICATIONS PROCESSOR INTERFACE

The interface to an Applications Processor/Adjunct (AP) is provided by the following three circuit packs:

- Interface 1

- Interface 2

- Interface 3

As shown in Figure 1, these circuit packs are connected to the M bus. Interface 1 and Interface 2 are connected by the S bus. The S bus contains 16 data, 24 address, 5 parity, 10 interrupt, and 11 control lines. The S bus is located on the backplane of the control carrier and provides the medium for the SPE to transfer data to or from the AP.

#### Interface 1

The Interface 1 circuit pack serves as a gateway between the SPE's local M bus and the S bus by performing the decoding and arbitration necessary to allow communication with the Interface 2 circuit pack. When the SPE indicates that it wishes to perform an operation, the Interface 1 circuit pack secures the M bus for the SPE to lock out Interface 2 from the local M bus. The SPE then puts the address of the location it wishes to access onto the M bus.

The Interface 1 circuit then determines if this a local address or that of Interface 2 (remote address). If it is a local address, the cycle continues in a normal manner with the Interface 1 remaining in an unchanged state for the duration of the process. If it is a remote address, the Interface 1 circuit allows the SPE to gain access to the S bus. The process is reversed if Interface 2 is attempting to access the SPE. When this happens, the Interface 1 circuit blocks the SPE from its own M bus, allowing Interface 2 clear access to it.

The Interface 1 circuit pack consists of the following circuitry (see Figure 21):

- S bus decoder and arbitration circuitry

- . M bus decoder and arbitration circuitry

- · Control circuit

- XACK/Clock fail circuit

- · Bus buffers

- · Parity circuit

- · Spend circuit

- I/O bus circuit

Figure 21. Interface 1 Circuit

# S Bus Decoder and Arbitration Circuit

The S bus arbitration circuit determines whether Interface 2 or the SPE will actually be allowed to gain control of the S bus. The decoder monitors the S bus address, data, and command leads to determine when the Interface 1 circuit is addressed. The decoder also determines whether the SPE or the Interface 2 requesting the S bus has the highest priority.

## M Bus Decoder and Arbitration Circuit

The M bus arbitration circuit determines whether a local command or an S bus cycle accessing the local memory has priority. The decoder circuit is a 32-bit input decoder that determines when the Interface 1 circuit is being addressed on the M bus.

#### Control Circuit

The control circuit provides internal board signals that are used to control the various functions performed by the Interface 1 circuit pack.

#### XACK/Clock Fail Circuit

The transfer acknowledge (XACK) circuit tells the SPE or the Interface 2 when to terminate a cycle. The clock fail circuit checks for the presence of the S bus clock signal.

#### **Bus Buffers**

The bidirectional bus buffers connect all address, data, and command lines to both the M bus and the S bus. The direction of these buffers is determined by whether or not the SPE is acting as a source or destination for the transfer being performed.

## **Parity Circuit**

Even parity is used on both the address and data bus. This circuit checks the signals at the M bus destination after they are sent across the S bus by the Interface 2 or the SPE. The parity bits never appear on the M bus.

## Spend Circuit

The spend circuit is a 16 microsecond timer that causes a timeout to occur if the SPE does not get the S bus within 16 microseconds of request. Once the S bus is obtained, the spend timer is reset.

#### I/O Bus Circuit

The I/O bus circuit interfaces the Interface 1 I/O (ID, vintage, and NMI registers) to the SPE's M bus.

#### Interface 2

The Interface 2 circuit pack handles message traffic between the SPE and the AP. Its other functions include handling BX.25 protocol and supporting Call Detail Recording and Reporting (CDRR), Leave Word Calling, and Message Center. The Interface 2 circuit pack communicates with the SPE by means of the S bus and the Interface 3 circuit pack by means of the M bus.

The Interface 2 circuit pack consists of the following circuitry (see Figure 22):

- · Processor and timing circuit

- M bus buffers

- . Decoders/ACYL circuit

- Local Cycle Arbitrator

- I/O Ports

- DRAM control circuit

- DRAM

- · Memory buffers and ROM

- NMI and LEDs

- XACK/WAIT state circuit

- Parity circuit

- S bus interface (locks/gates/enable) circuit

- S bus arbitrator

- S bus interface (interrupt queue)

- P/O S bus interface buffers

- S bus interface buffers

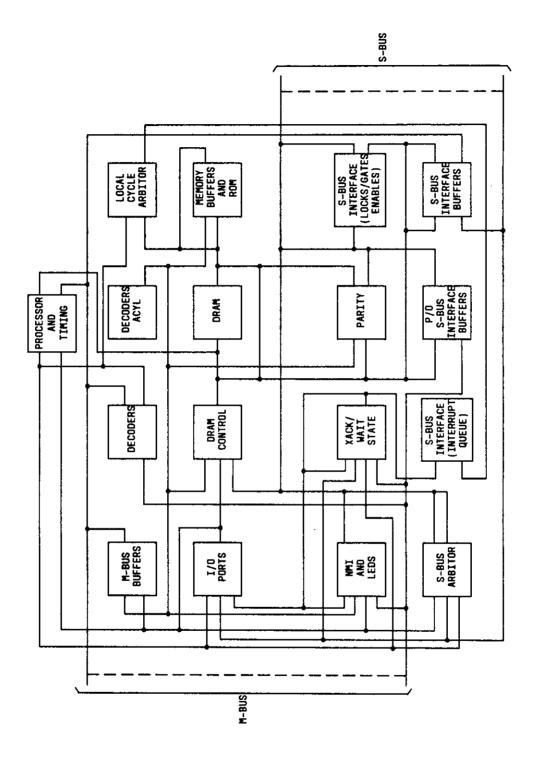

Figure 22. Interface 2 Circuit

# **Processor and Timing Circuit**

The processor and timing control circuit provides all timing and control signals necessary to provide basic functions for the entire circuit pack. It decodes basic board transactions, initiates board reset, provides address and data decoding, and controls circuit pack sanity.

#### M Bus Buffers

These buffers interface the processor circuit to the M bus. They receive or transmit address and control information between the Interface 2 circuit pack and any other circuit packs connected to the M bus.

#### Decoders

The decoders detect processor ID's and certain S bus address bits to determine interrupts and remote addresses. They also handle decoding that determine whether S bus gates are locked or unlocked and the on/off cycle of the red LED on the front of the circuit pack.

# Decoders/ACYL Circuit

This set of decoders handles decoding for commands, on-board timers, and non-maskable interrupts (NMIs). They decode on-board operations such as memory or programmable read-only memory (PROM) chip selects and determine whether an operation is on board or off board.

### Local Cycle Arbitor

This arbitor controls whether the Interface 2 circuit pack or a remote processor has access to the Interface 2 circuit pack's local memory.

#### I/O Ports

The I/O ports connect the local peripherals on the Interface 2 circuit pack.

#### **DRAM Control Circuit**

This circuit provides all timing and control functions for the on-board 128 kb dynamic RAM (DRAM) circuit.

### DRAM

This is the 128 kb local DRAM.

### Memory Buffers and ROM

The ROM can only be accessed by the Interface 2 circuit pack and is used after reset to initialize the board, run diagnostics, and provide a monitor.

#### NMI and LEDs

The Interface 2 circuit pack supports 12 non-maskable interrupts (NMIs) and 8 maskable interrupts. An eight bit read/write I/O port controls the LEDs on the front of the circuit pack and the sanity timer mask.

#### XACK/WAIT State

This circuit monitors every bus cycle and sends a transfer acknowledge signal to a source processor indicating the requested transfer has been completed. Depending on the activity, a timeout may occur or wait states are inserted.

#### S Bus Interface (Locks/Gates/Enables)

This is the Interface 2 circuit pack S bus control section. It determines if the Interface 2 circuit pack's access to the S bus is locked or unlocked.

#### S Bus Arbitor Circuit

This circuit determines whether the SPE or the Interface 2 requesting the S bus will actually be allowed to gain control of the bus and use it. This is determined on a first come, first served basis.

### S Bus Interface (Interrupt Queue)

This circuit stores the ID of the SPE that sent a message to Interface 2. The IDs are stored here until the Interface 2 circuit pack services the queue.

#### P/O Bus Interface Buffers

This set of buffers are used to interface command and parity check bits to the S bus.

#### S Bus Interface Buffers

These bidirectional buffers connect all address and data lines to both the M bus and S bus. The direction of these buffers is determined by whether or not Interface 2 is acting as a source or destination for the particular transfer being performed.

#### Interface 3

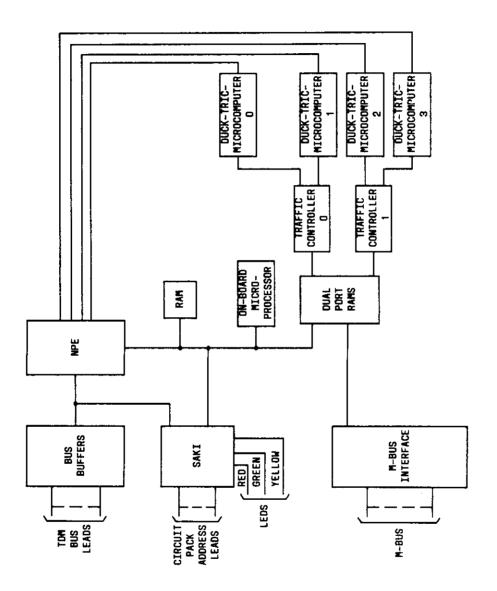

The Interface 3 circuit pack provides a link between the TDM bus and the Interface 2 circuit pack. Circuits on the Interface 3 circuit pack terminate the DCP and provide some link level support for the Interface 2 circuit pack. The Interface 3 circuit pack contains four separate ports.

The Interface 3 circuit pack consists of the following circuitry (see Figure 23):

- · Common circuitry

- Bus buffers

- SAKI

- NPE

- On-board microprocessor with external RAM

- . M bus interface circuit

- Traffic controller circuits and dual-port RAM

- DUCK-TRIC-Microcomputers

## Common Circuitry

The Interface 3 common circuitry provides the same general function as the intelligent port common circuitry.

# M Bus Interface Circuit

This circuit provides address decoding and chip select logic as well as a transfer acknowledge (XACK) signal during memory and I/O accesses from the M bus. Also included in this circuit is the interrupt latch and interrupt line drivers. The interrupt latch guarantees sufficient hold time for the programmable interrupt controller in the Interface 2 circuit pack.

# Traffic Controller and Dual-Port RAM Circuits

The two traffic controllers provide the data terminal equipment (DTE) portion of the EIA interface. The dual-port RAMs provide shared memory interface to the Interface 2 circuit pack.

## **DUCK-TRIC-Microcomputers**

There are four identical DUCK-TRIC-Microcomputer circuits on the Interface 3 circuit pack. The microcomputer handles the control portion of the DCP link. Under firmware control, the microcomputer handles EIA updates and DCP handshaking. The DUCK generates and interprets DCP clock update messages, and provides the client interface portion of the data module. The TRIC multiplexes the data stream from the DUCK and the control stream from the microcomputer and provides an interface to the network for the data module.

Figure 23. Interface 3 Circuit

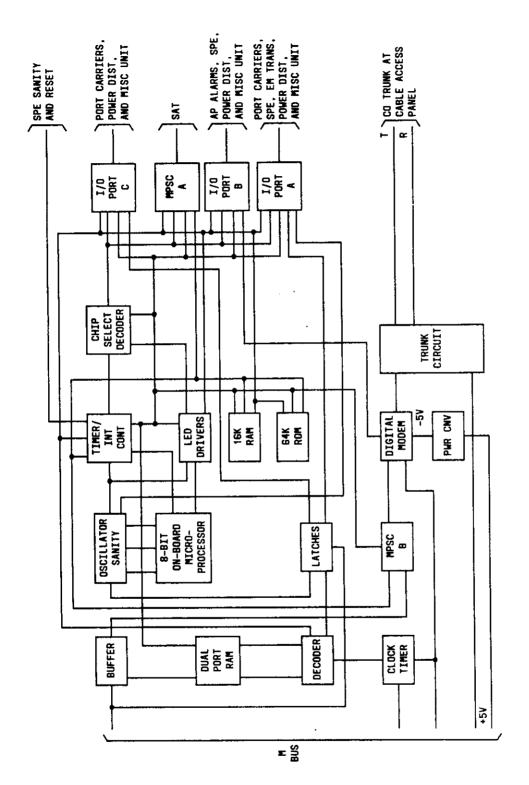

# MAINTENANCE CIRCUIT

#### General

The Maintenance circuit pack is a peripheral processor for the SPE. The Maintenance circuit pack communicates with the SPE on the M bus via dual port RAM and I/O registers. The I/O registers are accessed by the SPE using I/O read and write for high speed polling and backup communications. Two dedicated leads between the Maintenance circuit pack and the SPE provide signaling for the GO-TO-SLEEP command that disables the SPE. The leads also allow the Maintenance circuit pack to monitor SPE sanity.

The Maintenance circuit pack functions as follows:

- Originates alarms to the Initialization and Administration System (INADS) via a trunk circuit located on the circuit pack

- Includes a digital modem for reliable synchronous communication with INADS

- · Provides alarm LEDs for system status

- Provides emergency transfer switch and emergency transfer control

- · Monitors and controls the reset condition and sanity of the SPE

- Monitors and controls the power units and battery charger

- · Monitors the cabinet environment

- Provides maintenance circuit pack diagnostics

- Provides direct access to dedicated system administration terminal (SAT)

When the Maintenance circuit pack is initialized, the SPE sends the Maintenance circuit pack necessary administration data (INADS phone number, product identification, and software vintage).

# SPE Monitoring and GO-TO-SLEEP Control

The SPE is automatically reset every time a sanity time-out occurs. The SPE controls the recovery after a reset. The Maintenance circuit pack monitors the SPE sanity timer and, if the rate of sanity time-outs are excessive, the SPE is shutdown via the GO-TO-SLEEP signal. This signal becomes active after the threshold has been reached. When the threshold is reached, the Maintenance circuit pack will do the following:

- Put the SPE to sleep

- Invoke emergency transfer

- Notify INADS

- Update alarm LED status